深度学习应用芯片规划,时间缩短至平均6小时内

文/陈根

英特尔创始人之一戈登·摩尔曾说过,集成电路上可以容纳的晶体管数目大约每经过18个月便会增加一倍。换句话说,处理器的性能每隔两年就会翻一倍。这句话作为经验之谈,一定程度上揭示了信息技术发展的迅猛,后来成为著名的“摩尔定律”。然而,随着制程的不断演进,无法自动布局规划已成为芯片突破的一个重要挑战,这一定律在近年来也有所放缓。

近日,来自美国加州谷歌研究院的科学家,通过一种深度强化学习方法完成了芯片的布局设计。原本人类专家需要花费数周时间完成的过程,现在平均6小时内就能完成,速度超过28倍。

一般情况下,微芯片的面积约为几十到数百毫米平方,在一块指甲盖大小的硅片上排列并互连了数十亿个晶体管。每个芯片上包含数了千万个逻辑门(称为标准单元),以及数千个存储块(称为宏块或宏)。

单元和宏块通过数十公里的布线互连以实现设计的功能,它们的位置对设计结果至关重要,因为相应的位置会在很大程度上影响芯片的处理速度和电源效率。到目前为止,尤其是在布局规划方面还没有任何自动化尝试,它常常是由专业的人类工程师在数周或数月内努力工作而出。

在芯片的设计过程中,全局布线是最复杂和耗时的阶段之一,也是决定芯片整体性能的关键。针对这一板块的缺失,谷歌的研究团队研究开发出一种机器学习工具,用来加速布局规划的流程。

科学家们将芯片的布局规划部分设计为一个强化学习问题,开发出可完成的芯片设计神经网络。这个智能网络会把布局规划看作一个棋盘游戏:元件是“棋子”,放置元件的画布是“棋盘”,“获胜结果”则是根据一系列评估指标评出的最优性能(评估基于一个包含1万例芯片布局的参考数据集)。这种方法能在6小时内设计出与人类专家不相上下或是更好的可行芯片布局,提速超过了28倍。

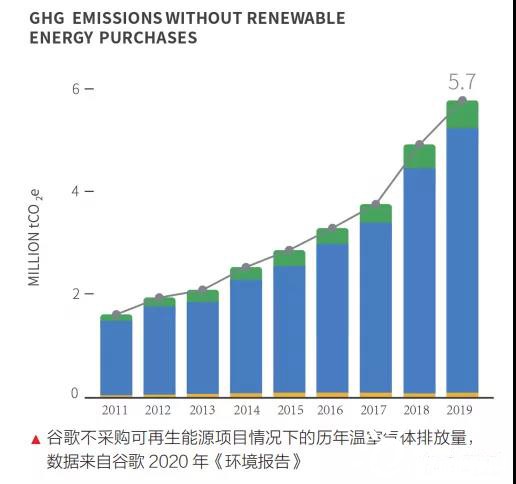

该设计不仅大大节约了时间成本,还打破了芯片开发计划中可以探索解决的方案数量。目前,研究团队的布局规划方案已经被应用在谷歌下一代AI处理器的设计上,未来该研究或也能用于优化城市规划、疫苗测试等。

-

不放弃芯片!华为坚持海思研发

2021-06-15 -

永鼎股份有大动作!定增募资 10.8亿!加速向上游芯片的渗透

2021-06-14 -

传台积电考虑在美国建造首家芯片封装工厂!

2021-06-14 -

华能辛店电厂深度调峰取得重大突破

2021-06-11 -

谷歌研究新突破:6小时完成芯片设计

2021-06-10 -

华为大力推动国内芯片产业,只为破解外国技术垄断!

2021-06-10 -

索尼WF-1000XM4降噪豆发布:首发自研V1芯片!

2021-06-09 -

杀回芯片赛道!传小米重组团队,正在和相关IP供应商谈判

2021-06-09 -

车厂加注芯片产业,比亚迪参投源卓广电

2021-06-09 -

国产内存新玩家:兆易创新自研DRAM芯片量产

2021-06-07 -

芯片价格飙涨5倍:“买不起”、“买不到”成常态

2021-06-07 -

苹果最新芯片曝光:性能强得没边!

2021-06-07 -

深度解读思必驰语音合成技术,干货满满

2021-06-04 -

一文了解深度学习模型VAE的时序性解耦

2021-06-04 -

2021-2026年通信电源系统行业深度分析

2021-06-04